# DDR6: THE NEXT EVOLUTION IN HIGH-PERFORMANCE MEMORY TECHNOLOGY

#### **INTRODUCTION**

Since the commercial debut of DDR5 in 2021 – aligning with AMD Ryzen 7000 and Intel Alder Lake architectures—memory technology has evolved to support exponential increases in bandwidth and efficiency. DDR5 achieved substantial improvements over DDR4, including dual sub-channel design and increased transfer rates. However, the rising computational demands of AI model training, real-time analytics, and immersive gaming have underscored the need for a new generation of memory.

DDR6 is being standardized by the JEDEC JC-42.3 subcommittee, with a projected release of Specification 1.0 in 2025. Initial prototypes from leading DRAM manufacturers indicate transformative capabilities in throughput, power optimization, and memory architecture.

# **DEVELOPMENT TIMELINE AND STANDARDIZATION PROCESS**

The progression of DDR standards follows a consistent cadence of approximately five-year intervals, with each generation doubling the maximum data transfer rate. The timeline for DDR6 development is as follows:

- 2018-2020: DDR5 standardization and release

- 2021–2023: Broad DDR5 adoption across servers, desktops, and mobile platforms

- 2024: JEDEC circulates the initial DDR6 draft specification

- Q2 2025: Expected ratification of DDR6 Specification 1.0

- Q4 2025-Q1 2026: Anticipated formal publication of the final standard

#### Table 1. Evolution of DDR Standards

| Standard | Max JEDEC Data Rate (MT/s) | Year Introduced |  |

|----------|----------------------------|-----------------|--|

| DDR      | 400                        | ~2000           |  |

| DDR2     | 800                        | ~2003           |  |

| DDR3     | 1,866                      | ~2007           |  |

| DDR4     | 3,200                      | ~2014           |  |

| DDR5     | 6,400                      | ~2020           |  |

| DDR6     | ≥12,800 (Projected)        | ~2025–2026      |  |

This structured standardization process ensures that DDR6 will be interoperable across CPU, SoC, and DIMM suppliers, accelerating time to market once finalized.

#### TECHNICAL INNOVATIONS AND KEY FEATURES

#### **Memory Speed and Bandwidth**

DDR6 is expected to double maximum data transfer rates relative to DDR5. Projections indicate:

- Standard baseline speeds: ≥12,800 MT/s

- Overclocked modules: ≥15,000–17,000 MT/s

These speeds will enable memory bandwidths exceeding 134 GB/s per DIMM, supporting increasingly data-intensive applications.

#### **Architectural Enhancements**

DDR6 introduces multiple architectural innovations designed to improve throughput and efficiency:

- **Four Memory Channels:** DDR6 employs four 16-bit sub-channels per DIMM (vs. DDR5's two 32-bit channels), enhancing parallelism and reducing latency.

- New Pinout Configurations: Revised layouts optimized for high-frequency signaling.

- Adaptive Refresh Mechanism: Dynamically scales refresh cycles based on workload and temperature.

- **Sideband Communication:** Adds dedicated signaling for telemetry, power management, and error correction.

- Command Truth Band (CTB): Improves command integrity and minimizes latency.

- Expanded Memory Addressing: Supports higher density modules and large dataset processing.

- Advanced CA Topologies: Includes Decision Feedback Equalization (DFE) for reliable high-speed signaling.

#### **Power Efficiency Improvements**

DDR6 is projected to achieve significant power reductions:

- Lower Core Voltage: <1.1 V (vs. DDR5's 1.1 V and DDR4's 1.2 V).

- Dynamic Voltage and Frequency Scaling (DVFS): Real-time tuning of power consumption.

- Advanced Power Management: On-die regulators and adaptive refresh.

These advances will be essential for sustainable data centers, edge computing, and mobile devices.

## **COMPREHENSIVE TECHNICAL COMPARISON**

| Parameter                        | DDR               | DDR2              | DDR3              | DDR4            | DDR5             | DDR6<br>(Projected)           |

|----------------------------------|-------------------|-------------------|-------------------|-----------------|------------------|-------------------------------|

| JEDEC Max Data<br>Rate (MT/s)    | 400               | 800               | 1,866             | 3,200           | 6,400            | ≥12,800                       |

| Overclocked<br>Potential (MT/s)  | ~550              | ~1,066            | ~2,133            | ~4,000          | ~8,400           | ≥15,000–17,000                |

| Typical Voltage                  | 2.5 V             | 1.8 V             | 1.5 V (1.35 V LP) | 1.2 V           | 1.1 V            | <1.1 V                        |

| Burst Length                     | 2, 4, 8           | 4, 8              | 8                 | 8               | 16               | 16                            |

| Prefetch Buffer                  | 2n                | 4n                | 8n                | 8n              | 16n              | ≥16n                          |

| Channels per<br>DIMM             | 1                 | 1                 | 1                 | 1               | 2                | 4                             |

| Sub-channel<br>Width             | 64 bits           | 64 bits           | 64 bits           | 64 bits         | 32 bits          | 16 bits                       |

| DIMM Max<br>Bandwidth            | ~3.2 GB/s         | ~6.4 GB/s         | ~14.9 GB/s        | ~25.6 GB/s      | ~51.2 GB/s       | ≥134 GB/s                     |

| CAS Latency<br>(Cycles)          | 2-3               | 3-6               | 5–11              | 10–19           | 20-40            | TBD<br>(Expected ≥40)         |

| Refresh Modes                    | Auto/Manual       | Auto/Manual       | Auto/Manual       | Auto/Manual     | Auto/Manual      | Adaptive Refresh              |

| Power Saving<br>Features         | Basic             | Partial Array SR  | Partial Array SR  | DBI, CA Parity  | DVFS, On-die ECC | DVFS, Sideband<br>Telemetry   |

| Signal Integrity<br>Enhancements | Basic termination | ODT               | Fly-by topology   | DFE, ODT        | DFE, ODT         | DFE, CTB,<br>Sideband         |

| Error Correction                 | No (Optional ECC) | No (Optional ECC) | Optional ECC      | Optional ECC    | On-die ECC       | Enhanced On-die<br>ECC        |

| Typical Power<br>Consumption     | High              | Moderate          | Moderate          | Lower           | Lower            | Significantly<br>Lower        |

| Target Markets<br>(Initial)      | Desktop           | Desktop, Server   | Desktop, Server   | Server, Desktop | Server, Desktop  | HPC, Al, Cloud,<br>Enterprise |

# **APPLICATION DOMAINS**

DDR6's performance and efficiency improvements make it especially well-suited for:

- Al Training and Inference: Large parallel datasets and low-latency retrieval.

- Cloud and Hyperscale Data Centers: High throughput to support virtualized workloads.

- High-Performance Gaming: Real-time computation and rendering.

- Enterprise Analytics: Scalable data pipelines.

- Edge and Mobile Computing: Power-sensitive environments.

#### **APPLICATION AND ADOPTION TRENDS**

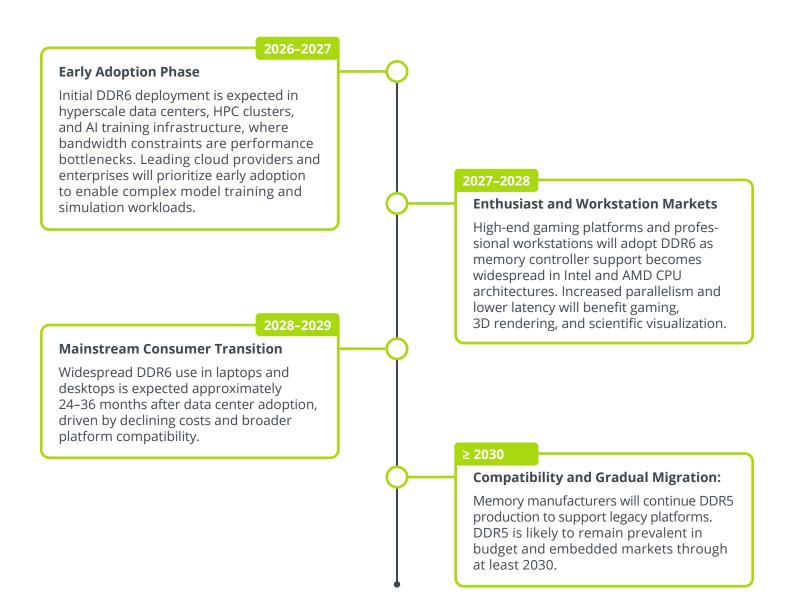

The transition to DDR6 is anticipated to follow the pattern observed in prior DRAM migrations, characterized by an initial phase of limited deployment in specialized domains before mainstream adoption.

#### **Acceleration Factors:**

- Al and Data Analytics Workloads: Expanding model complexity drives earlier adoption.

- Advanced Gaming Requirements: Demand for low-latency memory.

- **Edge Computing Proliferation:** Memory bandwidth constraints in decentralized inference scenarios.

Overall, DDR6 adoption is expected to proceed more rapidly than DDR5 but may still require 5 – 6 years to reach majority penetration.

#### **CONCLUSION:**

DDR6 represents the next transformative advance in DRAM technology, combining unprecedented bandwidth, improved power efficiency, and architectural flexibility. While the specification is pending JEDEC ratification, consensus indicates DDR6 will soon become foundational to high-performance computing ecosystems across Al, cloud, gaming, and enterprise workloads.

The coming years will define the trajectory of memory innovation – and DDR6 is positioned to lead that evolution.

#### **REFERENCES:**

- 1. JEDEC Solid State Technology Association. DDR5 SDRAM Specification JESD79-5. JEDEC, 2019.

- 2. JEDEC JC-42.3 Subcommittee. DDR6 Draft Specification, 2024.

- 3. Samsung Electronics. Next-Generation DRAM Roadmap White Paper, 2025.

- 4. Micron Technology. DDR6 Memory Architecture Overview, Technical Brief, 2025.

- 5. Intel Corporation. Advances in Memory Subsystem Design for Al Workloads, 2025.

- 6. AMD. Signal Integrity Strategies for Next-Gen DRAM, 2025.

- 7. IEEE. "Dynamic Voltage Scaling for High-Performance DRAM," IEEE Transactions on Circuits and Systems, 2023.

- 8. SK hynix. Adaptive Refresh Techniques in DDR6 Memory, 2025.

- 9. Samsung Electronics. Future Memory Architectures for Exascale Computing, 2024.

#### **ABOUT US**

MEMPHIS Electronic has been in the memory business for over 30 years. Due to our focus on memory only, we developed into a Memory Competence Center with an unmatched line card of over 18 different memory manufacturers (Samsung, Nanya, SK Hynix, Winbond, Huawei, SkyHigh, Ramxeed, Intelligent Memory, Apacer, Longsys, ESMT, Biwin and many more). We combine this with comprehensive supply chain solutions.

From legacy to latest components and modules, from standard to specialty memories – if it's a memory, we can help. Memory experts in 17 locations worldwide provide regional support and manufacturer recommendations, to ensure customers find the most suitable technology solution for every project.

# **MEMPHIS LOCATIONS**

### **CONTACT US**

For further information, data sheets or samples, please reach out. We are only an email away: <a href="mailto:sales@memphis.de">sales@memphis.de</a>